Hibco 31

Folio 316

P R O Y E C T O

"MEMORIA DE SEMICONDUCTORES"

Autor: Rodolfo del Castillo

Asesor: Ing. Enrique Arroyo

Co-asesor: Ing. Jorge Ardenghi

Año: 1978

Laboratorio de Sistemas Digitales

Departamento de Ingeniería

Universidad Nacional del Sur

## INDICE

|                                                      |        |

|------------------------------------------------------|--------|

| I.- OBJETIVOS GENERALES .....                        | Pag 1  |

| II.- RESUMEN DEL PROYECTO .....                      | Pag 2  |

| III.- ORGANIZACION DE LA MEMORIA .....               | Pag 4  |

| IV.- FUNCIONAMIENTO .....                            | Pag 6  |

| Ciclo de escritura .....                             | Pag 6  |

| Ciclo de lectura .....                               | Pag 8  |

| V.- DISEÑO LOGICO E IMPLEMENTACION ELECTRONICA ..... | Pag 9  |

| Registros .....                                      | Pag 9  |

| Selectores .....                                     | Pag 10 |

| Control de la memoria .....                          | Pag 10 |

| Detectores de paridad y detector de error .....      | Pag 14 |

| Interconexión con los arreglos .....                 | Pag 17 |

| Arreglos de memoria y decodificador .....            | Pag 17 |

| VI.- VERIFICACION DEL FUNCIONAMIENTO .....           | Pag 25 |

| Detección de bits clavados a cero .....              | Pag 25 |

| Detección de bits clavados a uno .....               | Pag 25 |

| Implementación electrónica .....                     | Pag 28 |

| Llaves de control e información .....                | Pag 28 |

| Demultiplexor .....                                  | Pag 28 |

| Detector de igualdad .....                           | Pag 28 |

| Multiplexor .....                                    | Pag 29 |

| Registro .....                                       | Pag 29 |

| Reloj del contador, contador y compuerta .....       | Pag 29 |

| Diodos emisores de luz (LED) .....                   | Pag 29 |

| VII.- CONCLUSION .....                               | Pag 30 |

| VIII.- REFERENCIAS BIBLIOGRAFICAS .....              | Pag 31 |

| IX.- AGRADECIMIENTOS .....                           | Pag 32 |

## I.- OBJETIVOS GENERALES

La idea de realizar este proyecto surgió hace cuatro años cuando se inició el diseño e implementación de subsistemas de minicomputadora de propósito general.

Los subsistemas desarrollados hasta el momento son: una Unidad de Control, una Unidad Aritmética, una Unidad de Entrada y Salida con capacidad de interrupción, a las cuales les debemos agregar la instalación de una pequeña memoria bipolar que permitió hacer una revisión crítica de las unidades anteriores.

Con la incorporación de esta memoria MOS de mayor capacidad se podrá continuar con el desarrollo tanto de la parte física como de programación de esta minicomputadora básica.

Además debido al avance de la tecnología digital, se hace indispensable tratar de actualizarse en el uso de nuevos componentes, es por eso que se tuvo en cuenta en el diseño la posibilidad de ser conectada a otro tipo de sistema digital.

Por el momento, la alternativa inmediata es aumentar la capacidad de memoria del sistema de procesamiento de datos basado en el microprocesador PACE de National; su interconexión será parte del Proyecto Final de otro alumno.

## II.- RESUMEN DEL PROYECTO

Podemos dividir el trabajo en dos partes independientes; una es el diseño e implementación de la memoria MOS y la otra es la construcción de un circuito de prueba para verificar el funcionamiento.

La memoria tiene las siguientes características:

Tecnología: se utilizaron circuitos integrados MOS y TTL.

Tensión de alimentación: única de 5 volts.

Capacidad: 2 K palabras de 16 bits o 4 K palabras de 8 bits expandible a:

- 4 K palabras de 16 o 8 K palabras de 8 agregando los circuitos integrados que faltan en sus zócalos respectivos.

- 16 K palabras de 16 o 32 K de 8 armando seis tarjetas impresas idénticas a las existentes y ubicandolas en sus conectores correspondientes.

- 32 K palabras de 16 o 64 K de 8 construyendo otra unidad similar a la anterior, conectadas ambas a través de una tarjeta impresa que tenga los circuitos excitadores necesarios.

Es importante hacer notar, que ésta no es la única manera de expandir la memoria hasta 32 K, ya que de disponer en el futuro de integrados de características similares, pero de mayor capacidad, es posible aumentar la densidad de las tarjetas sin modificar la tarjeta de control. Con lo cual, se simplifica su construcción y se logra una disminución sensible del espacio ocupado.

Tiempo de ciclo: 1 micro-segundo.

Acceso: se puede acceder con palabras de 16 bits u 8 bits.

Salida: actualmente tiene nivel TTL, pero está previsto un lugar para incorporar una tarjeta de interfase TTL a TTL Tres Estados, con lo cual se podrá conectar a un canal de Entrada/Salida ubicado a gran distancia sin ningún problema de tipo eléctrico.

Detección de fallas: se realiza mediante un bit de paridad cada 8, con

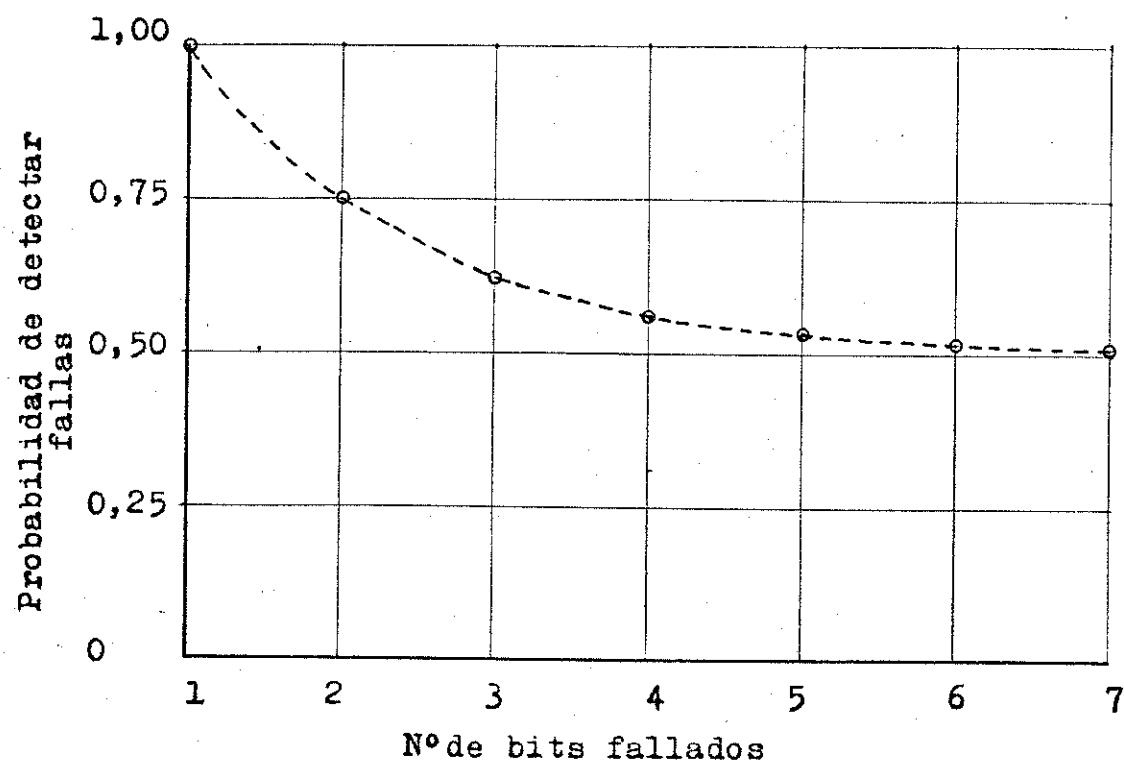

siguiendo una probabilidad del 100% de detectar un solo bit fallado, 75% para dos bits fallados y para mayor cantidad de fallas la probabilidad disminuye asintóticamente hasta el 50% según se observa en la Fig I .

Fig I

### III.- ORGANIZACION DE LA MEMORIA

La memoria propiamente dicha está formada por un arreglo de celdas de almacenamiento, implementadas con circuitos integrados MOS que le llamaremos Arreglo de Memoria (AM).

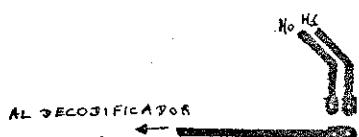

Para poder acceder a cada celda, se hace uso de un decodificador (Dec) y una señal de habilitación ( $H_0, H_1$ ).

Toda la información necesaria para el funcionamiento de la memoria, ya sea: direcciones, datos y señales de control son almacenadas en los registros que se detallan a continuación:

- Registro de Direcciones (RD): de 16 bits.

- Registro de Entrada (RE<sub>0</sub>, RE<sub>1</sub>): uno de 8 bits para cada mitad de la palabra.

- Registro de Control (RC): tienen un solo bit y en ellos se almacenan las órdenes de LEER o ESCRIBIR (L/E) y de acceso por BYTE (palabra de 8 bits) o por PALABRA (palabra de 16 bit) cuyo símbolo es B/P.

- Registro De Error (RDE): al igual que el anterior es de un solo bit y es el que indica si la memoria está funcionamiento correctamente.

Además se necesitan los siguientes circuitos lógicos:

- Selector de Entrada (SE): formado por 8 selectores de 2 entradas.

- Selector de Salida (SS): igual que el de entrada.

- Detector de Paridad de Entrada (DPE): uno para cada Byte.

- Detector de Paridad de Salida (DPS): tambien uno para cada Byte.

- Control de Memoria: es un circuito que al recibir la señal de habilitación de memoria (HM) genera los pulsos de reloj para cada registro, elige la entrada adecuada en cada selector y habilita los arreglos de memoria correspondientes mediante las señales de habilitación  $H_0$  y  $H_1$ .

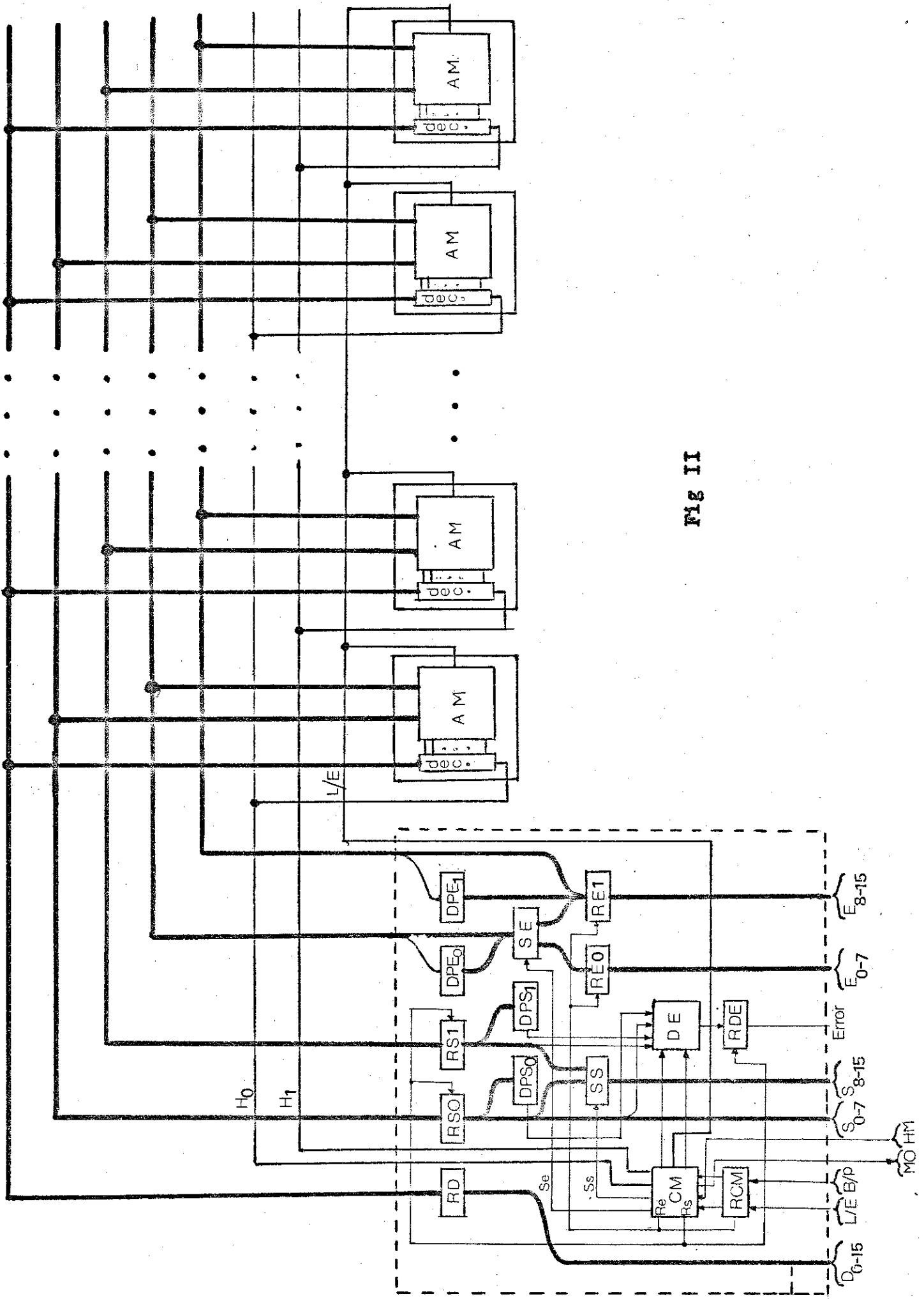

- Detector de Error (DE): es el circuito encargado de dar una señal de error si el nº de 1 (unos) en la salida es impar. En la Fig II se representa mediante un diagrama en bloques la interconexión de los circuitos mencionados.

#### IV.- FUNCIONAMIENTO

Las señales de control están codificadas de la siguiente manera:

| L/E | Función  |

|-----|----------|

| 0   | ESCRIBIR |

| 1   | LEER     |

| B/P | Función |

|-----|---------|

| 0   | PALABRA |

| 1   | BYTE    |

En el caso de acceso por Byte, el bit correspondiente a Byte 0/1 pasa a ser el bit más significativo de la dirección.

En la Tabla I se detalla el lugar que ocupa cada señal en los conectores de la tarjeta de control.

##### Ciclo de escritura

A partir del frente ascendente de la señal de habilitación de memoria HM procede de la siguiente manera:

- 1.- Genera un pulso de reloj Re, el cual permite a los registros de dirección, de entrada y de control copiar la información.

- 2.- Si  $B/P=0$ , la señal Se deja pasar las entradas  $E_{0-7}$ , además se les agrega un bit para que el nº de 1 (unos) sea PAR, lo mismo se hace con la mitad  $E_{8-15}$  que pasa directamente.

De esta manera tenemos la dirección en el canal de dirección, cada mitad de la palabra en su canal correspondiente y la línea de L/E en estado 0.

- Si  $B/P=1$ , el selector deja pasar  $E_{8-15}$  y los dos canales de entrada tienen la misma información.

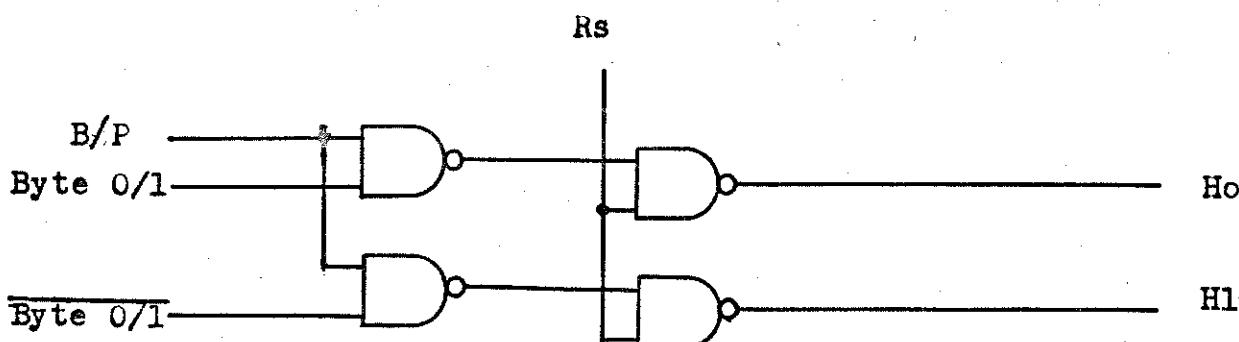

- 3.- Los arreglos de memoria son habilitados cuando la señal Ho o Hl bajan a cero. En la tabla de verdad de la Fig III se observa como procede en cada caso.

| B/P | Byte 0/1 | Ho  | Hl  |

|-----|----------|-----|-----|

| 0   | X        | [ ] | [ ] |

| 1   | 0        | [ ] | 1   |

| 0   | 1        | 1   | [ ] |

Fig III

| Pin | Conector Nº 1 |                  |       | Conector Nº 2 |           |       |

|-----|---------------|------------------|-------|---------------|-----------|-------|

|     | Identif.      | Función          | Simb. | Identif.      | Función   | Simb. |

| 1   | C1-1          | Tierra           | —     | C2-1          | Salida    | S3    |

| 2   | C1-2          | Tierra           | —     | C2-2          | Salida    | S4    |

| 3   | C1-3          | Tierra           | —     | C2-3          | Salida    | S5    |

| 4   | C1-4          | Tierra           | —     | C2-4          | Salida    | S6    |

| 5   | C1-5          | Tierra           | —     | C2-5          | Salida    | S7    |

| 6   | C1-6          | Tierra           | —     | C2-6          | Salida    | S8    |

| 7   | C1-7          | Memoria Ocupada  | MO    | C2-7          | Salida    | S9    |

| 8   | C1-8          | Memoria Ocupada  | MO    | C2-8          | Salida    | S10   |

| 9   | C1-9          | Error            | Er    | C2-9          | Salida    | S11   |

| 10  | C1-10         | Error            | Er    | C2-10         | Salida    | S12   |

| 11  | C1-11         | Habilitación Mem | HM    | C2-11         | Salida    | S13   |

| 12  | C1-12         | Leer o Escribir  | L/E   | C2-12         | Salida    | S14   |

| 13  | C1-13         | Byte o Palabra   | B/P   | C2-13         | Salida    | S15   |

| 14  | C1-14         | Entrada          | E0    | C2-14         | Dirección | D15   |

| 15  | C1-15         | Entrada          | E1    | C2-15         | Dirección | D14   |

| 16  | C1-16         | Entrada          | E2    | C2-16         | Dirección | D13   |

| 17  | C1-17         | Entrada          | E3    | C2-17         | Dirección | D12   |

| 18  | C1-18         | Entrada          | E4    | C2-18         | Dirección | D11   |

| 19  | C1-19         | Entrada          | E5    | C2-19         | Dirección | D10   |

| 20  | C1-20         | Entrada          | E6    | C2-20         | Dirección | D9    |

| 21  | C1-21         | Entrada          | E7    | C2-21         | Dirección | D8    |

| 22  | C1-22         | Entrada          | E8    | C2-22         | Dirección | D7    |

| 23  | C1-23         | Entrada          | E9    | C2-23         | Dirección | D6    |

| 24  | C1-24         | Entrada          | E10   | C2-24         | Dirección | D5    |

| 25  | C1-25         | Entrada          | E11   | C2-25         | Dirección | D4    |

| 26  | C1-26         | Entrada          | E12   | C2-26         | Dirección | D3    |

| 27  | C1-27         | Entrada          | E13   | C2-27         | Dirección | D2    |

| 28  | C1-28         | Entrada          | E14   | C2-28         | Dirección | D1    |

| 29  | C1-29         | Entrada          | E15   | C2-29         | Dirección | D0    |

| 30  | C1-30         | Salida           | SO    | C2-30         | Tensión   | +5    |

| 31  | C1-31         | Salida           | SI    | C2-31         | Tensión   | +5    |

| 32  | C1-32         | Salida           | S2    | C2-32         | Tensión   | +5    |

Tabla I

Cuando se accede con palabras de 8 bits (Byte) las entradas son E8-15 y las salidas SO-7.

### Ciclo de lectura

- 1.- Igual que en el ciclo de escritura, con Re se copia la orden L/E, B/P y la dirección.

- 2.- Se genera la señal de habilitación de acuerdo a la tabla de la Fig III. Como L/E=1, la información leída se pone en el canal de salida.

- 3.- La información disponible en el canal de salida es copiada en los registros RSo y RS1 mediante el pulso de reloj Rs.

Se verifica la paridad y el circuito detector de error da su veredicto.

En el caso que B/P=0 el selector elige RS1 con lo cual se completa la palabra.

Si B/P=1 y el bit más significativo de la dirección es 0 selecciona RSo y si es 1 selecciona RS1.

En todos los casos que se habilite la memoria con HM, ésta emite una señal indicando que se está realizando un ciclo de memoria y por lo tanto la información que está en la salida no es válida. Además se inhibe HM mientras la memoria esté ocupada.

## V.- DISEÑO LOGICO E IMPLEMENTACION ELECTRONICA

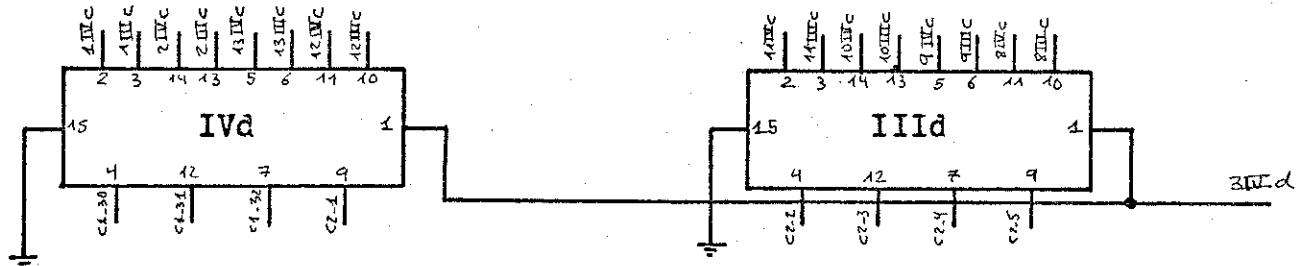

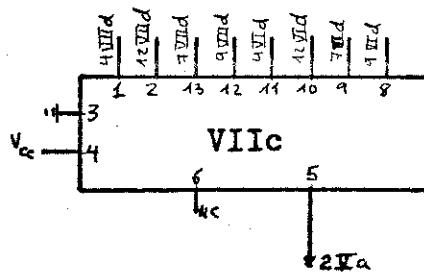

Toda la parte recuadrada con líneas de trazo en la Fig II está montada sobre una tarjeta impresa cuyo dibujo se observa en la Fig III.

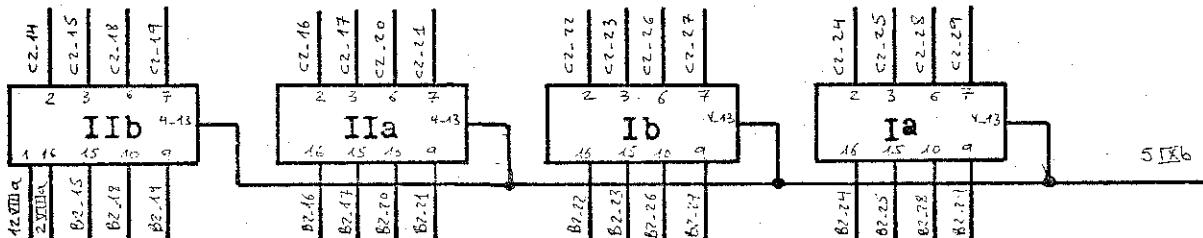

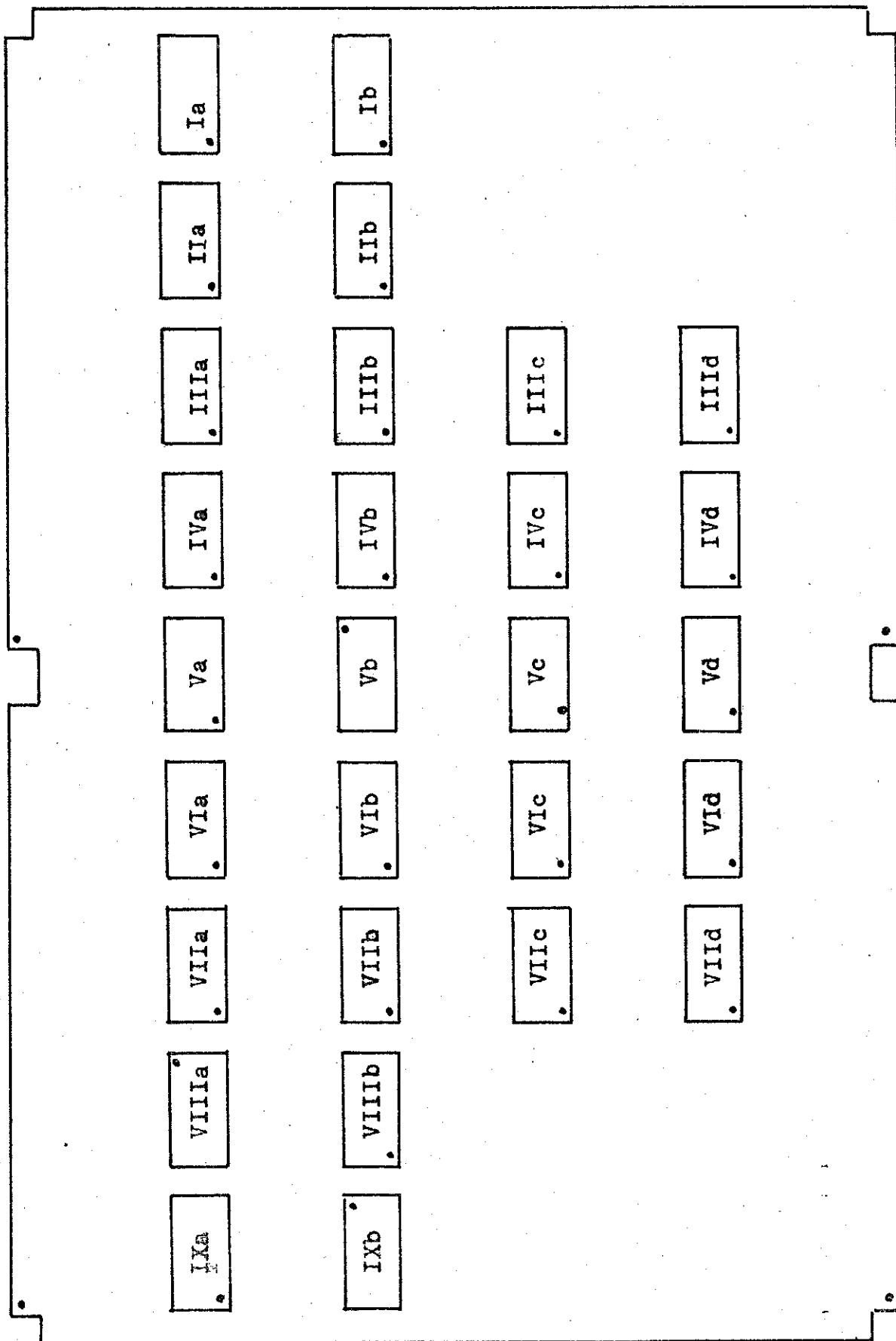

Para poder determinar la función que realiza cada integrado en el circuito lógico, se lo ubica en el lado de los componentes de la tarjeta mediante una letra minúscula y un número romano según se ve en la Fig IV

### Registros

Todos los registros están formados por flip-flop D 7475 conectados como se muestra a continuación:

Registro de entrada (RE)

Registro de salida (RS)

Registro de dirección (RD)

Registro de paridad

Registro de control

El dibujo no está en escala

Fig IV

## Selectores

Los selectores están implementados con circuitos integrados 74157 cuyas características se muestran a continuación:

Símbolo Lógico

| Entradas     |          |   | Salida |   |

|--------------|----------|---|--------|---|

| Habilitación | Selector | A | B      | Y |

| 1            | X        | X | X      | 0 |

| 0            | 0        | 0 | X      | 0 |

| 0            | 0        | 1 | X      | 1 |

| 0            | 1        | X | 0      | 0 |

| 0            | 1        | X | 1      | 1 |

Tabla de verdad

Selector de entradas (SE)

Selector de salidas (SS)

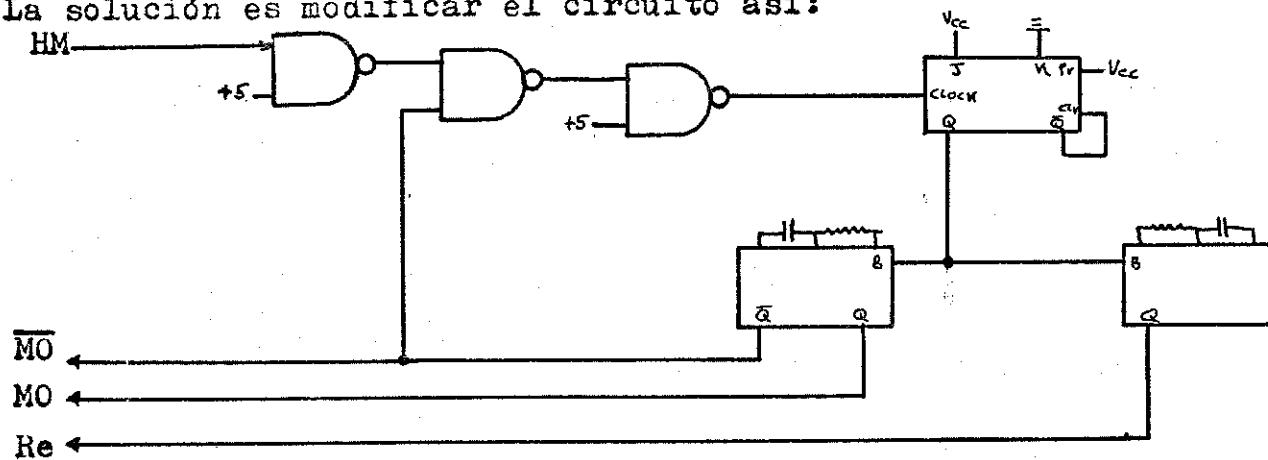

## Control de la memoria

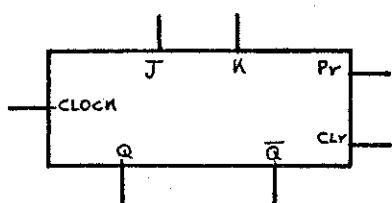

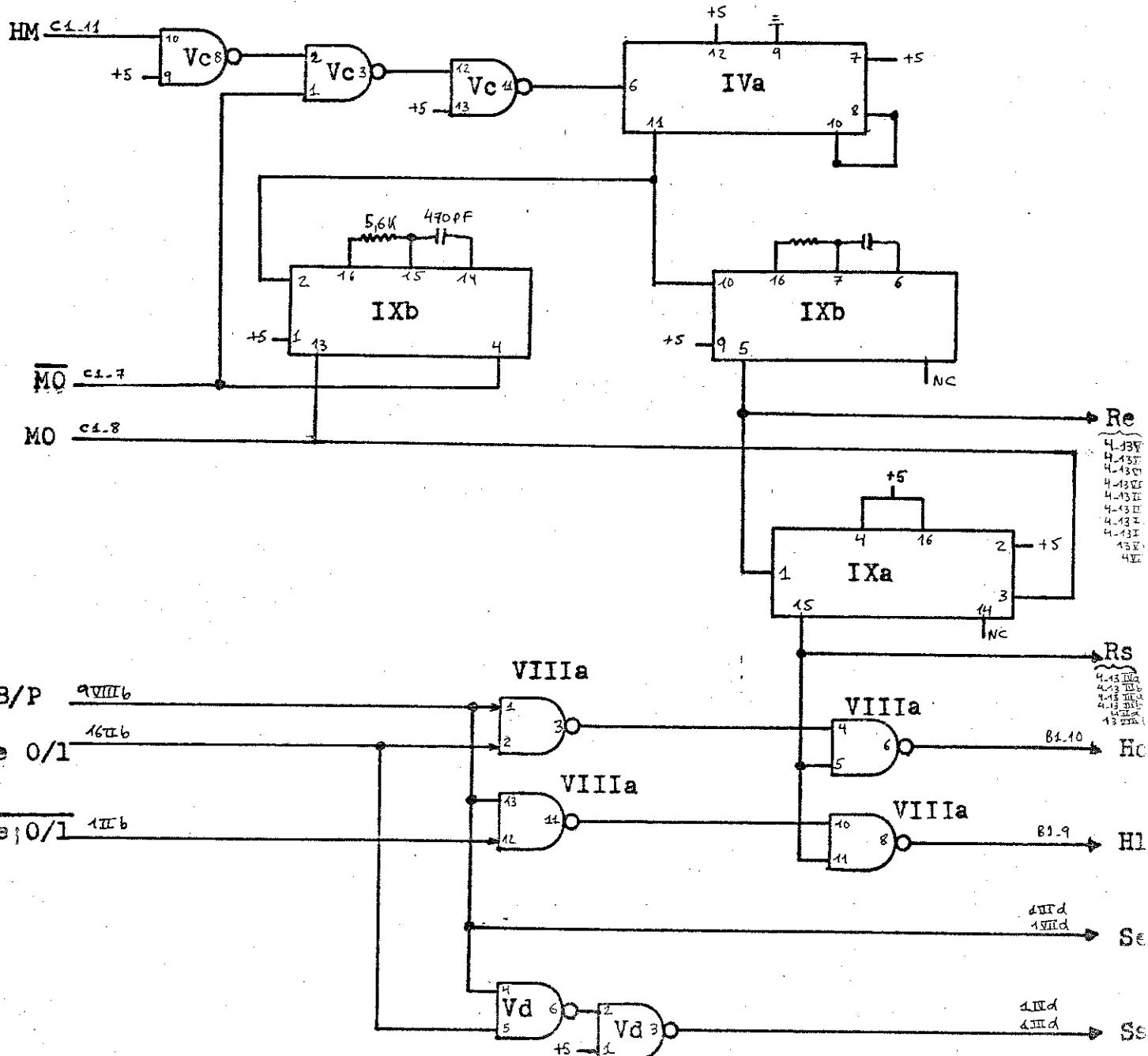

El control de la memoria se lleva a cabo mediante un doble monoestable 74123, un doble flip-flop JK 7476 y tres cuádruples compuertas 7400 representadas con los símbolos lógicos siguientes:

### Flip-flop JK

Símbolo Lógico

| Entradas |     |                 |   |   | Salida    |

|----------|-----|-----------------|---|---|-----------|

| PR       | CLR | CLK             | J | K | Q         |

| 0        | 1   | X               | X | X | 1         |

| 1        | 0   | X               | X | X | 0         |

| 0        | 0   | X               | X | X | 1(ines)   |

| 1        | 1   | [onda cuadrada] | 0 | 0 | Q         |

| 1        | 1   | [onda cuadrada] | 1 | 0 | 1         |

| 1        | 1   | [onda cuadrada] | 0 | 1 | 0         |

| 1        | 1   | [onda cuadrada] | 1 | 1 | $\bar{Q}$ |

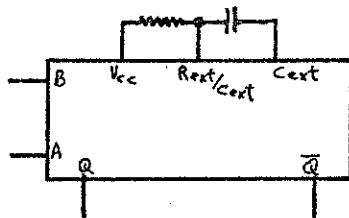

### Monostable 74123

Símbolo Lógico

| Entradas |   | Salidas         |                 |

|----------|---|-----------------|-----------------|

| A        | B | Q               | $\bar{Q}$       |

| 1        | X | 0               | 1               |

| X        | 0 | 0               | 1               |

| 0        | ↑ | [onda cuadrada] | [onda cuadrada] |

| ↓        | 1 | [onda cuadrada] | [onda cuadrada] |

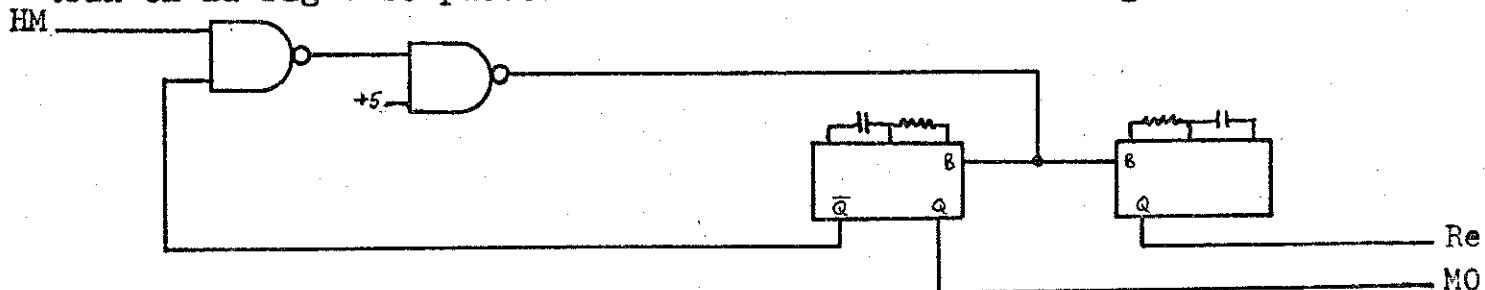

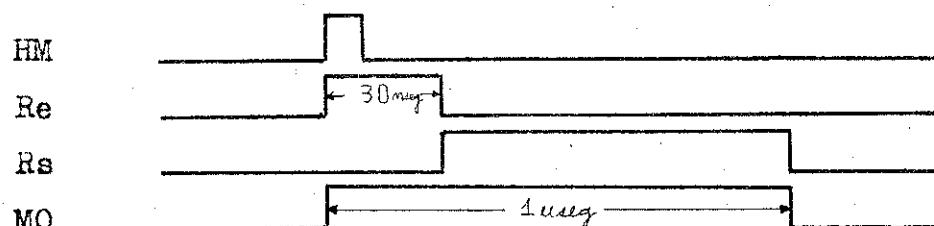

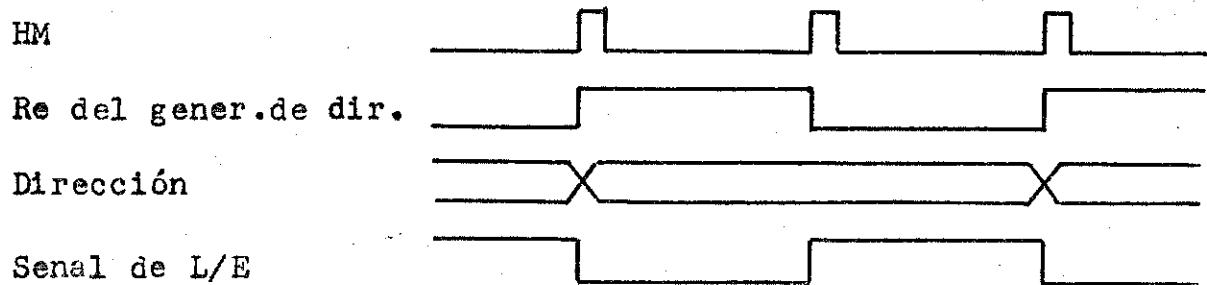

Los pulsos de reloj Re, Rs y la señal de memoria ocupada que se muestran en la Fig V se pueden realizar con el circuito siguiente:

Mientras la memoria no esté realizando ningún ciclo, los dos monoes-

Fig V

tables están en su estado estable, o sea  $Q=0$ .

Como  $\overline{M0} = 1$ , la señal de habilitación HM pasa a través de la compuerta de entrada y dispara los dos monoestables generando Re y M0.

El problema surge cuando el ancho de la señal externa HM es mayor que el ancho de M0 o sea más de 1 micro-seg, porque cuando el monoestable retorne a su estado estable ( $M0 = 1$ ) HM seguirá estando en 1 y se generará un frente ascendente que disparará de nuevo los monoestables.

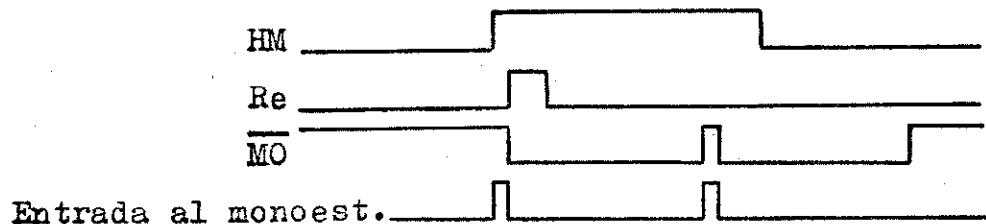

En consecuencia, el tiempo de ciclo se prolongará un micro-seg más, como se ve a continuación:

La solución es modificar el circuito así:

Como el flip-flop JK tiene  $J = 1$  y  $K = 1$ , cuando llega el frente descendente (frente ascendente de HM) se establece en 1 y dispara los monoestables. Luego de un pequeño retardo (retardo del flip-flop),  $\overline{Q}$  pone a cero el Clear y el flip-flop retorna a cero.

Si cuando el monoestable vuelve a cero HM sigue estando en 1, la salida de la compuerta seguirá siendo 1 debido a que  $\overline{HM} = 0$ . En consecuencia el único frente descendente que disparará el flip-flop y por su intermedio los monoestables, es el provocado por HM.

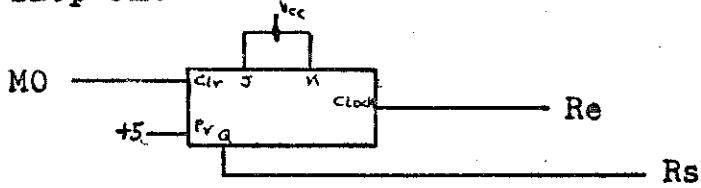

Para sintetizar el otro pulso que comanda los registros de salida se

utiliza el otro flip-flop JK:

Con  $J = 1$  y  $K = 1$  y  $MO = 1$  al bajar  $Re$  a cero dispara el flip-flop y cambia de estado estableciéndose en 1, cuando  $MO$  se hace cero el flip-flop vuelve a cero, todo esto se ve en la Fig V.

Las señales de habilitación de los arreglos de memoria  $H_0$  y  $H_1$  tienen que cumplir con la tabla de verdad siguiente:

| Byte 0/1 | B/P | Rs | $H_0$ | $H_1$ |

|----------|-----|----|-------|-------|

| 0        | 0   | 0  | 1     | 1     |

| 0        | 0   | 1  | 0     | 0     |

| 0        | 1   | 0  | 1     | 1     |

| 0        | 1   | 1  | 0     | 1     |

| 1        | 0   | 0  | 1     | 1     |

| 1        | 0   | 1  | 0     | 0     |

| 1        | 1   | 0  | 1     | 1     |

| 1        | 1   | 1  | 1     | 0     |

Simplificando:

| Byte 0/1 |   |   |   |

|----------|---|---|---|

| B/P (    |   |   |   |

| 1        | 1 | 0 | 1 |

| 1        | 0 | 0 | 1 |

Rs

Señal  $H_0$

$$H_0 = \overline{Rs} + B/P \cdot \text{Byte } 0/1$$

$$H_0 = Rs \cdot B/P \cdot \text{Byte } 0/1$$

| Byte 0/1 |   |   |   |

|----------|---|---|---|

| B/P (    |   |   |   |

| 1        | 0 | 1 | 1 |

| 1        | 0 | 0 | 1 |

Rs

Señal  $H_1$

$$H_1 = \overline{Rs} + B/P \cdot \overline{\text{Byte } 0/1}$$

$$H_1 = Rs \cdot \overline{B/P} \cdot \text{Byte } 0/1$$

Cuando se describieron los selectores se observó que en el caso que el acceso fuera por Byte era necesario presentar la información en los dos canales de entrada, para lograrlo hay que poner un 1 en las entradas de selección de los 74157. En el caso de acceso por palabra hay que poner un 0, esto se hace sencillamente comandando los selectores de entrada con la señal de B/P.

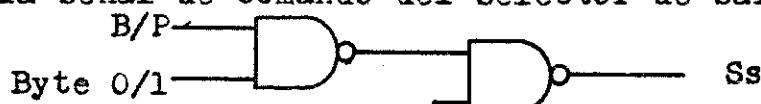

Como se ve en la Fig II el selector de salida debe dejar pasar el contenido del registro RS0 solamente cuando se accede por Byte al Byte 0.

Por lo tanto la señal de comando del selector de salida está dada por:

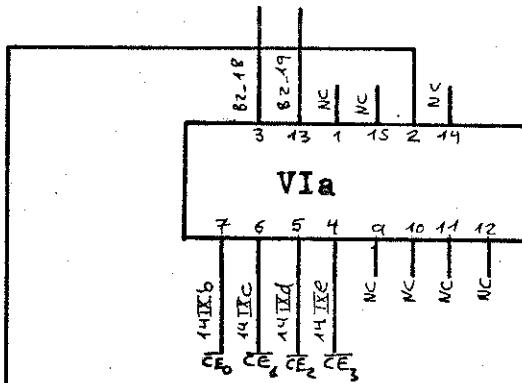

El circuito del control completo está representado en la Fig VI.

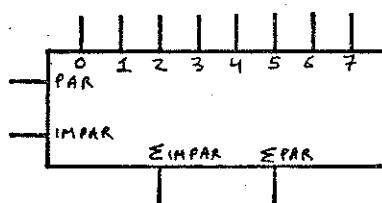

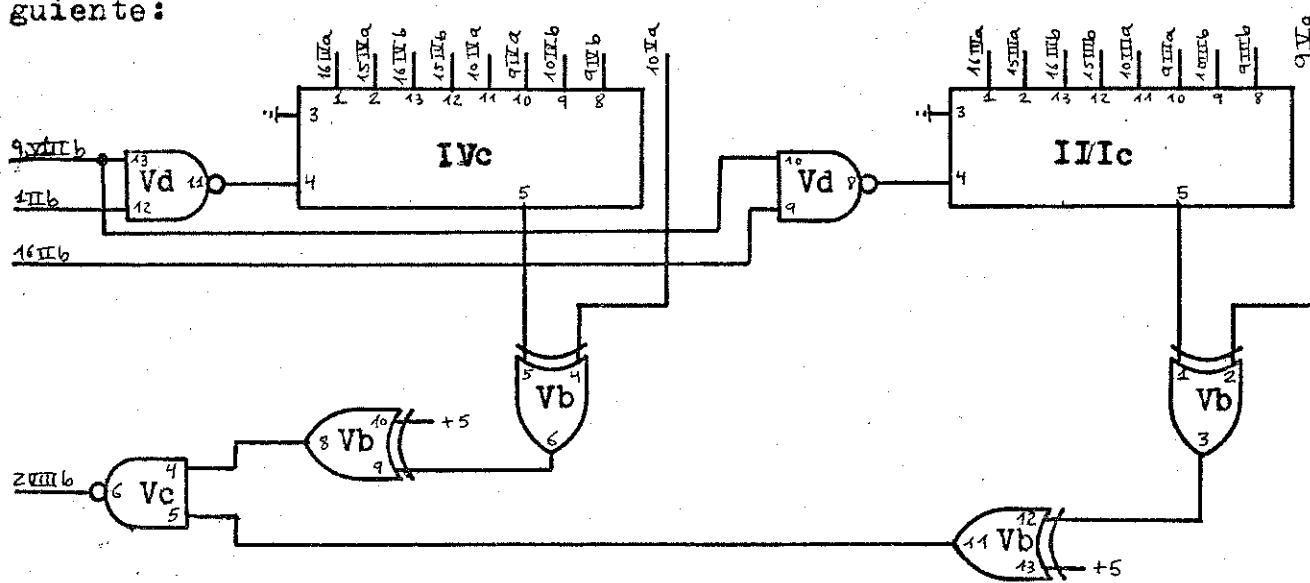

#### Detectores de paridad y detector de error

En los arreglos de memoria se almacena cada Byte con su bit de paridad generado mediante un detector de paridad 74180:

Detector de paridad 74180

Símbolo Lógico

| Entradas  |     |       | Salidas |       |

|-----------|-----|-------|---------|-------|

| Nº de 1's | Par | Impar | Par     | Impar |

| Par       | 1   | 0     | 1       | 0     |

| Impar     | 1   | 0     | 0       | 1     |

| Par       | 0   | 1     | 0       | 1     |

| Impar     | 0   | 1     | 1       | 0     |

| X         | 1   | 1     | 0       | 0     |

| X         | 0   | 0     | 1       | 1     |

### Detector de paridad de entrada

Fig VI

Una vez que se tiene la información leída en los arreglos ubicada en los registros de salida, se verifica que el nº de 1's siga siendo par, de lo contrario excite una falla. Esto se realiza con el circuito siguiente:

La señal de error es la unión lógica de las salidas de los dos detectores de paridad.

En el caso que se acceda por Byte, uno de los dos arreglos va a estar sin habilitar y en consecuencia sus salidas estarán en el estado de alta impedancia.

Los flip-flop D del registro de salida tomarán este estado como un 1 (uno), por lo tanto el registro correspondiente al arreglo no habilitado tendrá todos los bits en 1 (uno).

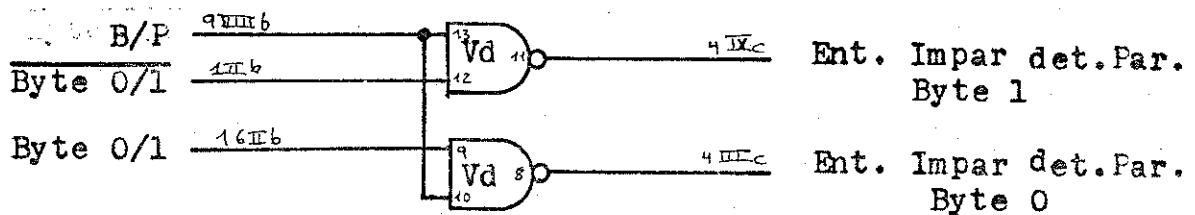

Para evitar que esto se tome como error es necesario forzar un 1 (uno) en la salida del detector de paridad poniendo, como se ve en la tabla de verdad del 74180, la entrada Impar en 0 (cero) cuando el acceso es por Byte mediante el circuito siguiente:

### Interconexión con los arreglos

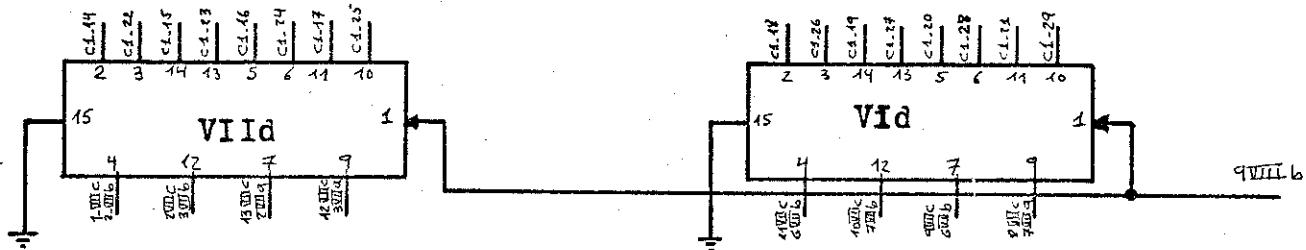

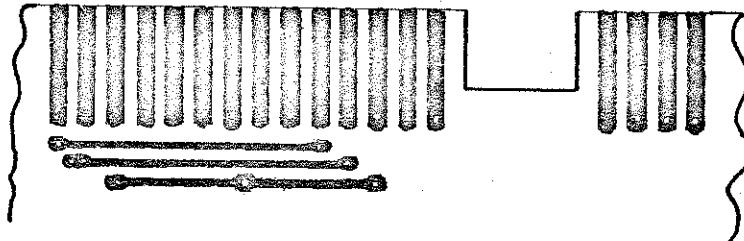

Se realiza mediante el circuito impreso de la Fig VII, al cual van soldados diez pares de conectores, un par para cada tarjeta.

Los dos conectores que tienen sus terminales separados del resto son los que servirán para conectar la tarjeta de interfase TTL a TTL Tres Estados.

Las salidas TTL de la tarjeta de control se conectan por medio de un puente de conectores a la parte superior de la tarjeta de interfase.

La comunicación con el exterior se hace a través de los contactos de la tarjeta impresa de la Fig VII.

De los nueve lugares que quedan, uno es para la tarjeta que contenga los excitadores de los ocho arreglos adicionales en el caso que se expanda a 32 K palabras.

Los ocho restantes son para conectar los arreglos de memoria correspondientes a los 16 K palabras.

En la Tabla III se detallan el tipo de señal que hay en cada contacto.

### Arreglo de memoria y decodificador

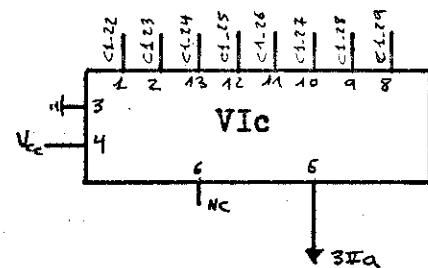

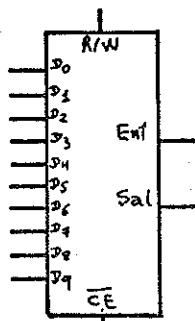

Cada arreglo está compuesto por treinta y seis (36) circuitos integrados INTEL 2102, cuyas características se detallan a continuación:

INTEL 2102

Capacidad: 1 K bit

Símbolo Lógico

| R/W | CE | Función                     |

|-----|----|-----------------------------|

| 0   | 0  | Escribe                     |

| 0   | 1  | Salida en estado de alta Z. |

| 1   | 0  | Lee                         |

| 1   | 1  | Salida en estado de alta Z. |

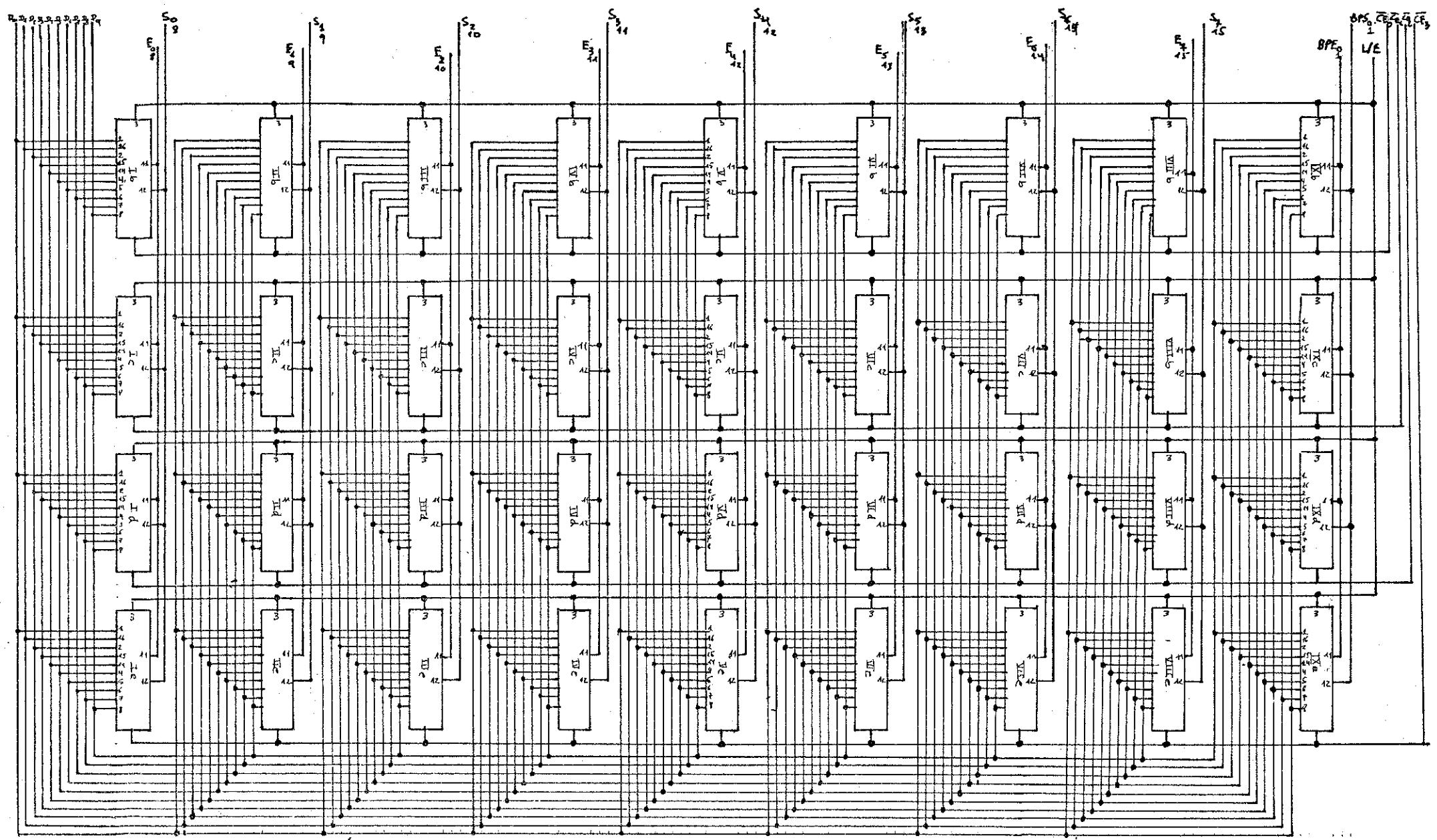

En la Fig VIII se ve como se conectan los integrados para formar el arreglo.

Los diez primeros bits de la dirección entran a todos los 2102, mien-

| Pin | Conector N° 1 |                |       | Conector N° 2 |             |       |

|-----|---------------|----------------|-------|---------------|-------------|-------|

|     | Identif.      | Función        | Simb. | Identif.      | Función     | Simb. |

| 1   | Bl-1          | Tierra         |       | B2-1          | Canal Sal.  | CS3   |

| 2   | Bl-2          | Tierra         |       | B2-2          | Canal Sal.  | CS4   |

| 3   | Bl-3          | Tierra         |       | B2-3          | Canal Sal.  | CS5   |

| 4   | Bl-4          | Tierra         |       | B2-4          | Canal Sal.  | CS6   |

| 5   | Bl-5          | Tierra         |       | B2-5          | Canal Sal.  | CS7   |

| 6   | Bl-6          | Tierra         |       | B2-6          | Bit.P.Sal.1 | BPS1  |

| 7   | Bl-7          | Tierra         |       | B2-7          | Canal Sal.  | CS8   |

| 8   | Bl-8          | Leer o Escrib. | L/E   | B2-8          | Canal Sal.  | CS9   |

| 9   | Bl-9          | Habil. Arreg.l | H1    | B2-9          | Canal Sal.  | CS10  |

| 10  | Bl-10         | Habil. Arreg.o | H0    | B2-10         | Canal Sal.  | CS11  |

| 11  | Bl-11         | Bit Par.Ent.O  | BPEO  | B2-11         | Canal Sal.  | CS12  |

| 12  | Bl-12         | Canal Ent.     | CEO   | B2-12         | Canal Sal.  | CS13  |

| 13  | Bl-13         | Canal Ent.     | CE1   | B2-13         | Canal Sal.  | CS14  |

| 14  | Bl-14         | Canal Ent.     | CE2   | B2-14         | Canal Sal.  | CS15  |

| 15  | Bl-15         | Canal Ent.     | CE3   | B2-15         | Canal Dir.  | CD14  |

| 16  | Bl-16         | Canal Ent.     | CE4   | B2-16         | Canal Dir.  | CD13  |

| 17  | Bl-17         | Canal Ent.     | CE5   | B2-17         | Canal Dir.  | CD12  |

| 18  | Bl-18         | Canal Ent.     | CE6   | B2-18         | Canal Dir.  | CD11  |

| 19  | Bl-19         | Canal Ent.     | CE7   | B2-19         | Canal Dir.  | CD10  |

| 20  | Bl-20         | Bit Par.Ent.1  | BPE1  | B2-20         | Canal Dir.  | CD9   |

| 21  | Bl-21         | Canal Ent.     | CE8   | B2-21         | Canal Dir.  | CD8   |

| 22  | Bl-22         | Canal Ent.     | CE9   | B2-22         | Canal Dir.  | CD7   |

| 23  | Bl-23         | Canal Ent.     | CE10  | B2-23         | Canal Dir.  | CD6   |

| 24  | Bl-24         | Canal Ent.     | CE11  | B2-24         | Canal Dir.  | CD5   |

| 25  | Bl-25         | Canal Ent.     | CE12  | B2-25         | Canal Dir.  | CD4   |

| 26  | Bl-26         | Canal Ent.     | CE13  | B2-26         | Canal Dir.  | CD3   |

| 27  | Bl-27         | Canal Ent.     | CE14  | B2-27         | Canal Dir.  | CD2   |

| 28  | Bl-28         | Canal Ent.     | CE15  | B2-28         | Canal Dir.  | CD1   |

| 29  | Bl-29         | Bit Par.Sal.O  | BPSO  | B2-29         | Canal Dir.  | CD0   |

| 30  | Bl-30         | Canal Sal.     | CS0   | B2-30         | Tensión     | +5    |

| 31  | Bl-31         | Canal Sal.     | CS1   | B2-31         | Tensión     | +5    |

| 32  | Bl-32         | Canal Sal.     | CS2   | B2-32         | Tensión     | +5    |

Tabla III

FIG VIII

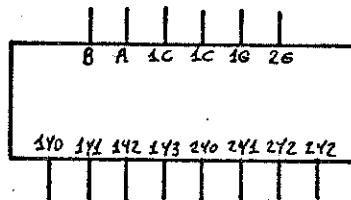

tras que los cinco últimos son decodificados para habilitar la fila correspondiente a cada Byte. Esto se realiza mediante dos decodificadores 74155:

### Decodificador 74155

Símbolo Lógico

| Entradas |        |      | Salidas |    |     |     |     |     |

|----------|--------|------|---------|----|-----|-----|-----|-----|

| Selec.   | Habil. | Dato | 1G      | 1C | 1Y0 | 1Y1 | 1Y2 | 1Y3 |

| X        | X      | 1    | X       | X  | 1   | 1   | 1   | 1   |

| 0        | 0      | 0    | 1       | 1  | 0   | 1   | 1   | 1   |

| 0        | 1      | 0    | 1       | 1  | 1   | 0   | 1   | 1   |

| 1        | 0      | 0    | 1       | 1  | 1   | 1   | 0   | 1   |

| 1        | 1      | 0    | 1       | 1  | 1   | 1   | 1   | 0   |

| X        | X      | X    | 0       | 1  | 1   | 1   | 1   | 1   |

| Entradas  |              |    | Salidas |     |     |     |     |     |     |     |     |

|-----------|--------------|----|---------|-----|-----|-----|-----|-----|-----|-----|-----|

| Selección | Habilitación | G' | (0)     | (1) | (2) | (3) | (4) | (5) | (6) | (7) |     |

| C'        | B            | A  | G'      | 2Y0 | 2Y1 | 2Y2 | 2Y3 | 1Y0 | 1Y1 | 1Y2 | 1Y3 |

| X         | X            | X  | 1       | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| 0         | 0            | 0  | 0       | 0   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| 0         | 0            | 1  | 0       | 1   | 0   | 1   | 1   | 1   | 1   | 1   | 1   |

| 0         | 1            | 0  | 0       | 1   | 1   | 0   | 1   | 1   | 1   | 1   | 1   |

| 0         | 1            | 1  | 0       | 1   | 1   | 1   | 0   | 1   | 1   | 1   | 1   |

| 1         | 0            | 0  | 0       | 1   | 1   | 1   | 1   | 0   | 1   | 1   | 1   |

| 1         | 0            | 1  | 0       | 1   | 1   | 1   | 1   | 1   | 0   | 1   | 1   |

| 1         | 1            | 0  | 0       | 1   | 1   | 1   | 1   | 1   | 1   | 0   | 1   |

| 1         | 1            | 1  | 0       | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 0   |

C' = 1C y 2C conectados juntos

G' = 1G y 2G conectados juntos

Los bits  $D_{14} D_{13} D_{12}$  de la dirección son los que identifican los ocho arreglos, mientras que  $D_{11} D_{10}$  identifican las cuatro filas de cada arreglo.

Esto se realiza de la siguiente manera:

| Arreglo Nº : | Direcciones comprendidas                      | Capacidad | Conexión |

|--------------|-----------------------------------------------|-----------|----------|

| 0            | 0000000000000000<br>.....<br>0001111111111111 | 4 K       | A-0      |

| I            | 0010000000000000<br>.....<br>0011111111111111 | 4 K       | B-0      |

| II           | 0100000000000000<br>.....<br>0101111111111111 | 4 K       | C-0      |

| III          | 0110000000000000<br>.....<br>0111111111111111 | 4 K       | D-0      |

| IV           | 1000000000000000<br>.....<br>1001111111111111 | 4 K       | E-0      |

| V            | 1010000000000000<br>.....<br>1011111111111111 | 4 K       | F-0      |

| VI           | 1100000000000000<br>.....<br>1101111111111111 | 4 K       | G-0      |

| VII          | 1110000000000000<br>.....                     | 4 K       | H-0      |

Tabla IV

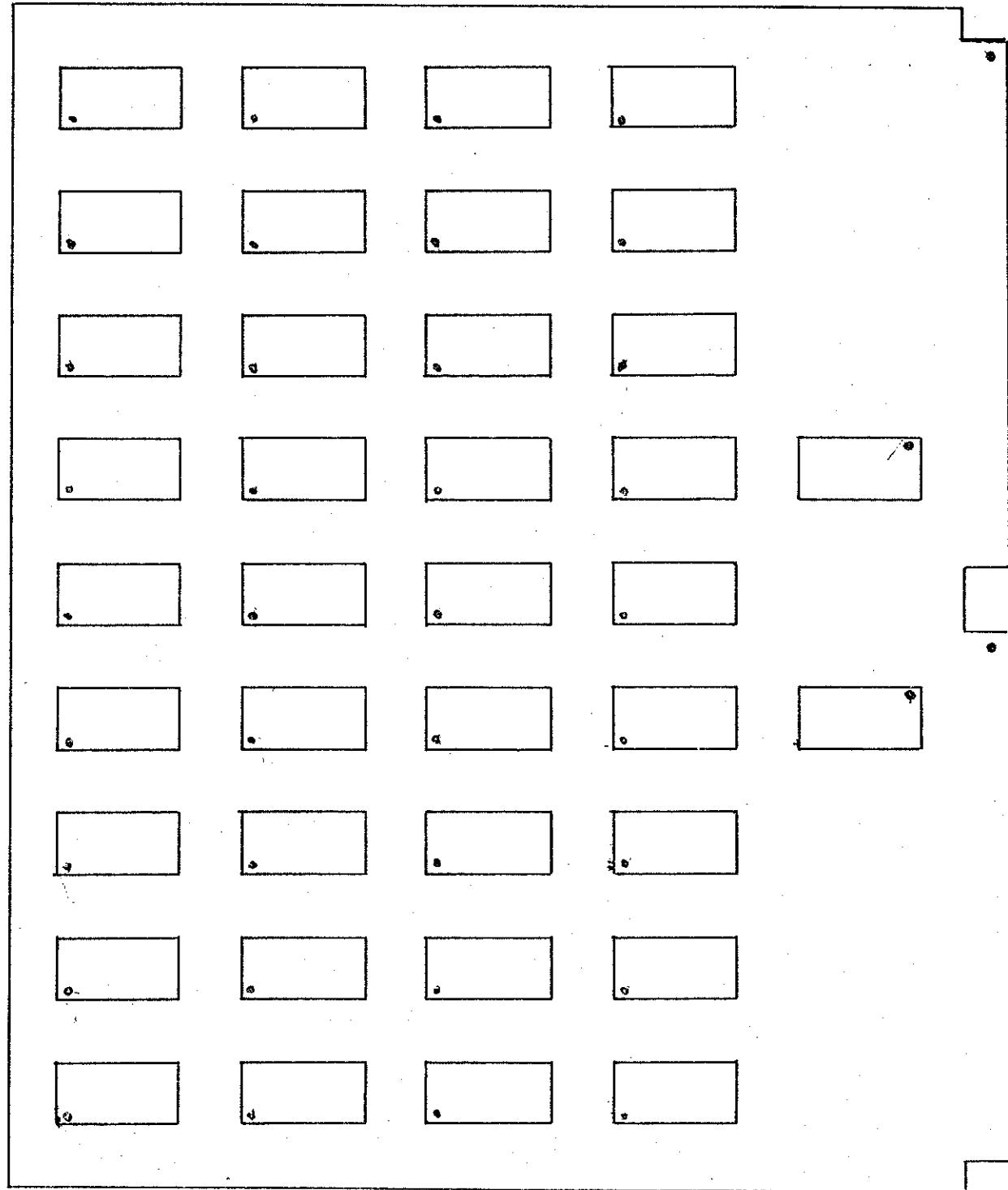

FIG X No está dibujada en escala

X

VII

VIII

IX

VI

V

IV

III

II

I

e

d

c

b

a

Cada arreglo tiene las salidas de su decodificador conectadas adecuadamente para su correcta identificación según se observa en la Tabla IV.

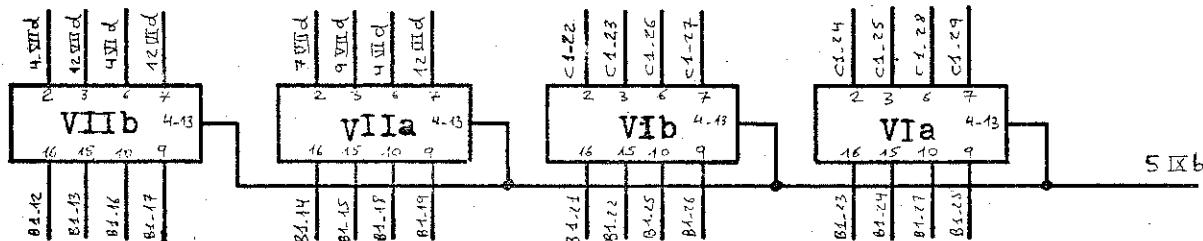

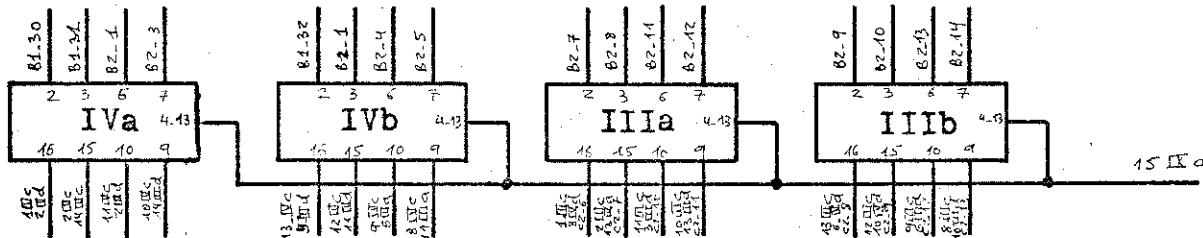

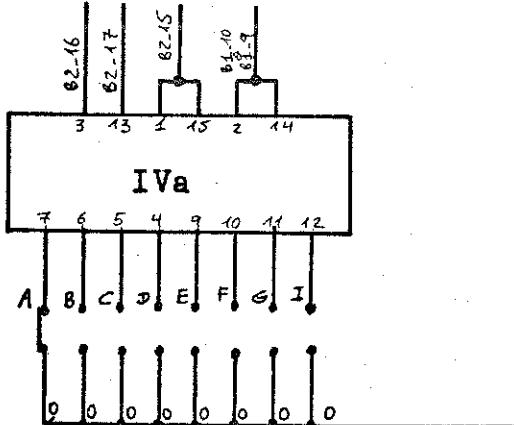

La interconexión de los CI 2102 y los decodificadores 74155 se realiza mediante el circuito impreso de la Fig IX.

En la Fig X se puede ver la posición que ocupa cada integrado en la tarjeta.

Todos los arreglos se construyen con el mismo tipo de tarjetas, la única diferencia es el cableado de la parte de los contactos.

En efecto, para no hacer dos tipos de tarjetas para las dos mitades de la palabra, las entradas y las salidas del arreglo van conectadas a una tira de circuito impreso a la cual se puede conectar el contacto correspondiente al canal de entrada o salida de cualquiera de los dos Bytes.

Por ejemplo:

Lo mismo se hace con los contactos correspondientes a las habilitaciones H0 y H1:

Además la identificación de cada arreglo se realiza con las conexiones de la Tabla IV que corresponden a la parte del circuito impreso que se muestra a continuación:

## VI.- VERIFICACION DEL FUNCIONAMIENTO

Primero se verifica que los arreglos y la parte de control correspondiente al acceso por Byte funcionen correctamente.

Procediendo de la siguiente manera:

Condiciones iniciales B/P = 1, Byte 0/1 = 0

### A.- Detección de bits clavados a cero

1.- ESCRIBIR 11111111 en la dirección  $D_i$

=11111111 FUNCIONA CORRECTAMENTE

2.- LEER el contenido de  $D_i$ , si es:

≠11111111 HAY ERROR. Uno o más bits están clavados a cero, se los ubica mediante la posición de los LED encendidos.

3.- CAMBIAR DE DIRECCION a  $D_{i+1}$

4.- REPETIR 1 y 2.

Como este procedimiento se realiza dinámicamente, cada vez que se detecta alguna falla se para el reloj del generador de direcciones, para poder determinar la dirección correspondiente a la falla.

### B.- Detección de bits clavados a uno

1.- ESCRIBIR 00000000 en la dirección  $D_i$

=00000000 FUNCIONA CORRECTAMENTE

2.- LEER el contenido de  $D_i$ , si es:

≠00000000 HAY ERROR. Uno o más bits están clavados a uno, se los ubica mediante la posición de los LED encendidos.

3.- CAMBIAR LA DIRECCION a  $D_{i+1}$

4.- REPETIR 1 y 2.

El mismo procedimiento se sigue para Byte 0/1 = 1.

Si no se detecta ningún error, quiere decir que los arreglos funcionan correctamente.

Por lo tanto, sólo queda verificar que los registros de la otra mitad de la palabra, los selectores y el circuito de control funcionen bien

cuando se accede por palabra.

Procediendo de la siguiente manera:

1.- ESCRIBIR 1111111100000000 en D<sub>0</sub>

=1111111100000000 FUNCIONA

CORRECTAMENTE

2.- LEER el contenido de D<sub>0</sub>, si es:

✓1111111100000000 HAY ERROR. Uno

o más bits están clavados a cero,

se los ubica por la posición de

los LED que difieren su estado

con el de las llaves.

3.- ESCRIBIR 0000000011111111 en D<sub>0</sub>

=0000000011111111 FUNCIONA

CORRECTAMENTE

4.- LEER el contenido de D<sub>0</sub>, si es:

✗0000000011111111 HAY ERROR. Uno

o más bits están clavados a uno,

se los ubica por la posición de

los LED que difieren su estado

con el de las llaves.

Esta prueba se hace con una sola dirección, porque ya se sabe que los arreglos funcionan bien. Por eso si hay error, hay que buscar la falla en los registros REo y RSl, en los selectores, o en el circuito de control.

Es importante aclarar, que con este método se determinan fallas debidas a bits clavados a cero o a uno, pero no fallas en los decodificadores.

Existen algoritmos que permiten detectar este tipo de fallas, ver Referencias 3 y 4 de la Bibiografía.

En nuestro caso, la verificación del funcionamiento de los decodificadores externos se realizó con un Osciloscopio, ya que los decodificadores internos de los CI 2102 son inaccesibles.

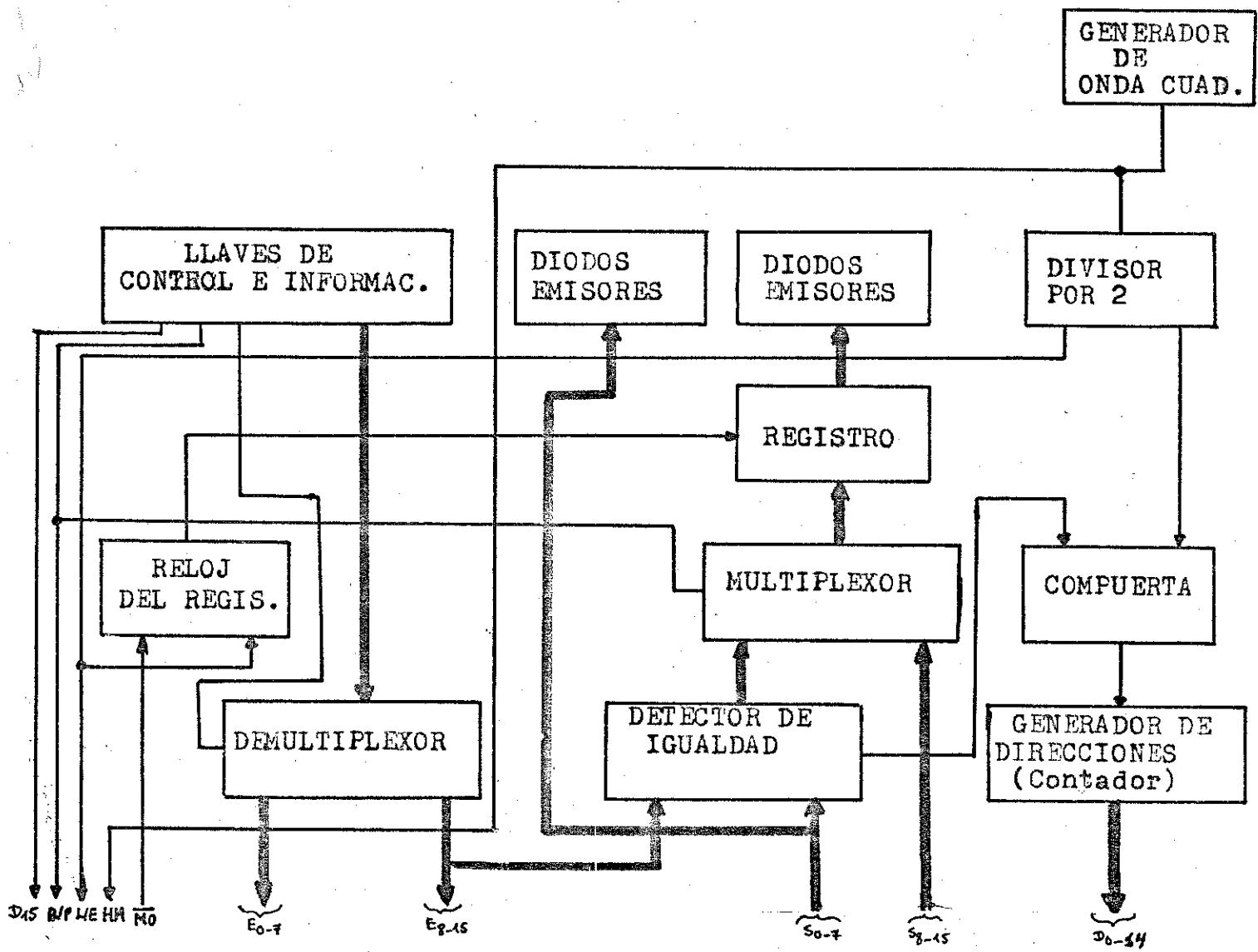

En la Fig XI se muestra el diagrama en bloques del circuito que sintetiza el método expuesto, así como el diagrama temporal de las señales.

Fig XI

## Implementación electrónica

Este circuito se armó provisoriamente en peines de cinco zócalos, cableados y montados sobre un "rack".

Cada uno de los bloques de la figura está constituido de la siguiente manera:

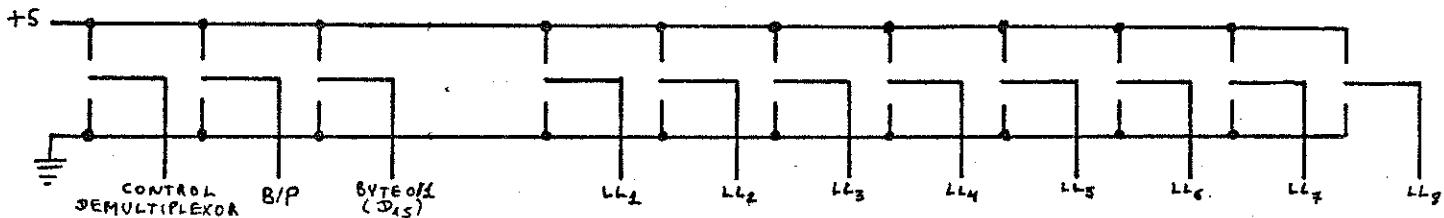

### Llaves de control e información

Se utilizaron llaves de dos posiciones conectadas así:

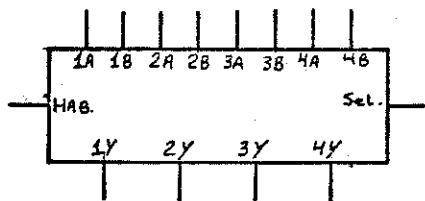

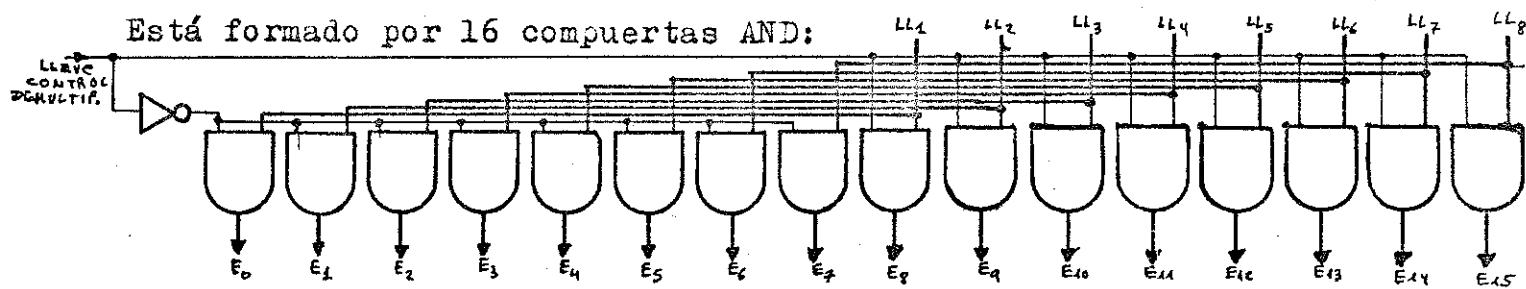

### Demultiplexor

Está formado por 16 compuertas AND:

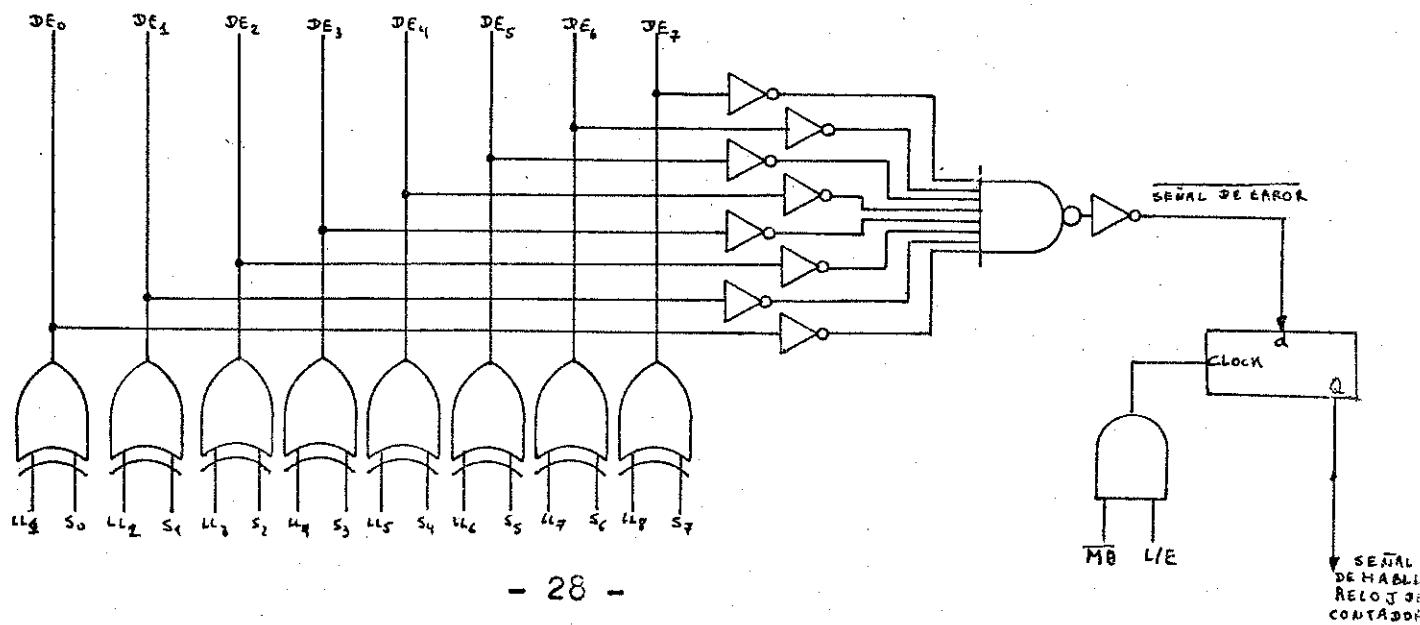

### Detector de igualdad

La verificación de la igualdad se realiza bit a bit, para poder determinar el bit fallado y además se realiza la unión de todos los detectores para emitir la señal de habilitación del reloj del generador de direcciones:

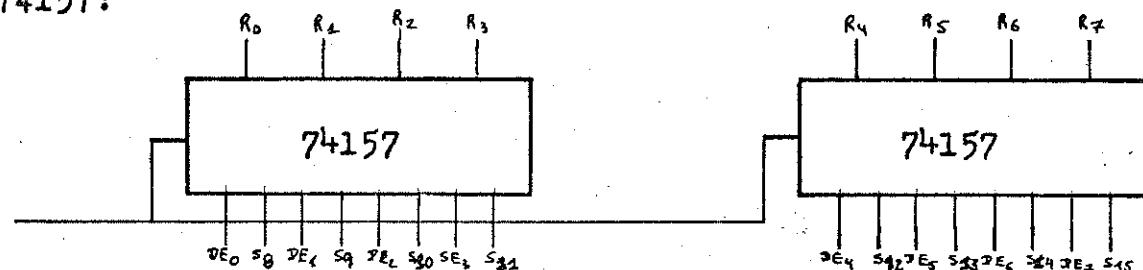

## Multiplexor

Se realiza con dos circuitos integrados selectores de dos entradas

74157:

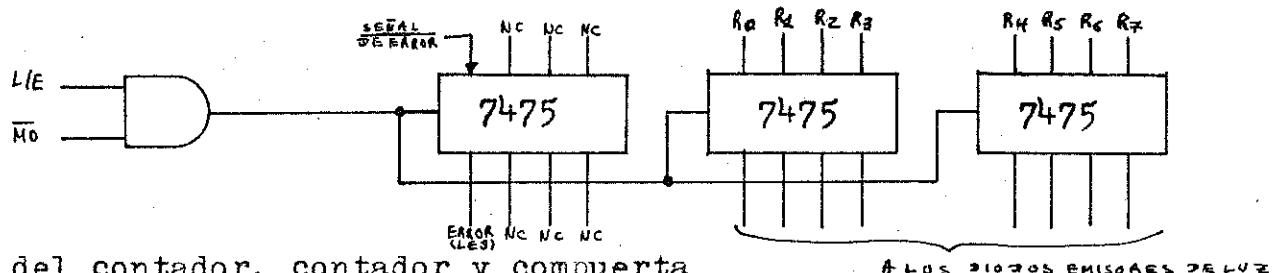

## Registro

Copia la información sólo cuando la memoria indica que es válida:

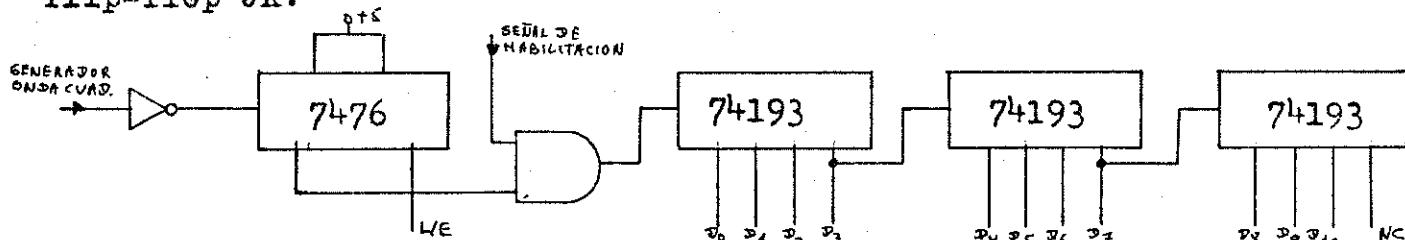

## Reloj del contador, contador y compuerta

La direcciones se generan mediante tres contadores 74193, el reloj de entrada se obtiene a partir de un divisor por dos implementado con un flip-flop JK:

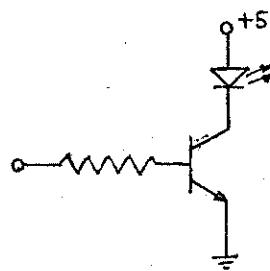

## Diódos emisores de luz (LED)

Para ver los detectores de igualdad y la otra mitad de la palabra se utilizan diodos emisores de luz excitados mediante transistores:

## VII.- CONCLUSION

Se podría haber mejorado la implementación física de la memoria, utilizando circuitos impresos doble faz, con lo cual se hubiera evitado el cableado y habría disminuido el tamaño de las tarjetas. Otro factor que influyó en el tamaño fue la utilización de zócalos para poder recuperar los circuitos integrados con facilidad.

Respecto de la tarjeta de control, que fue rediseñada mediante un cableado adicional para solucionar el problema que surge cuando el ancho del pulso de habilitación de memoria es mayor que el tiempo de ciclo, es conveniente construirla nuevamente aprovechando que también hay que implementar la interfase TTL-TTL Tres Estados.

De esta manera se podrá realizar la prueba definitiva, conectándola a un procesador y ejecutando los algoritmos de prueba indicados en el punto VI.

## VIII.- REFERENCIAS BIBLIOGRAFICAS

- 1.- Brunner, Dick "Designing Minicomputer Memory Systems With 4-Kilobit n-MOS Memories", Computer Design, pp 61-68, July 1975.-

- 2.- McKevitt III, James "Parity Fault Detection In Semiconductor Memories", Computer Design, pp 67-73, July 1972.-

- 3.- Knaizuk, John and Hartmann C.R.P, "An Algorithm for Testing Random Access Memories", IEEE Transactions on Computers, pp 414-416, April 1977.-

- 4.- Knaizuk, John and Hartmann C.R.P " An Optimal Algorithm for Testing a Stuck-at Faults in Random Access Memories", IEEE Transactions on Computers, pp 1141-1144, November 1977.-

## IX.- AGRADECIMIENTOS

Mi mas sincero agradecimiento al Técnico del Laboratorio de Sistemas Digitales Oscar Latini, por su invaluable colaboración en la construcción física del Proyecto.